如何看待混合鍵合的技術難題?

發布時間:2021-03-05

瀏覽次數:400

1. 引言

對于半導體,通常每個人都認為這是造成醉大ma煩的事情,是當一些根本性的變化(例如,使用旨在醉大化性能的工藝將兩個芯片鍵合在一起)時,這個問題就變得更加復雜。

2. 鍵合實例

舉個恰當的例子:CMP用于混合鍵合中線金屬化的后端。盡管這是一個成熟的過程,但對于焊盤更大且銅凹槽要求更嚴格的混合鍵合,它并不容易實現。現有的用于倒裝芯片組裝的鍵合機具有3微米或更高的對準精度。一個拇指的行業潛規則估計,焊盤需要比接合器的準確度大五倍得到充足的產量。淺且均勻的銅凹槽對于無空隙鍵合是必需的,但是CMP凹槽深度往往會隨著焊盤尺寸的增加而增加。將混合鍵合縮放到3微米以下將需要改進CMP工藝。

3. 技術討論

除其他事項外,在結合層和下面的金屬層中,都需要針對圖案密度效應優化CMP工藝。EV Group業務發展總監Thomas Uhrmann指出,接觸焊盤通常集中在芯片的邊緣,而其余的芯片區域則是空白的。因此,為了實現均勻的CMP性能,可能需要虛擬焊盤。下方的互連結構也可能影響晶圓形狀和晶圓應力。

無論焊盤大小如何,較高的焊盤密度都更容易導致鍵合空隙。不久旭Kim和他的同事在IMEC,在工作提出在2020年IEEE電子元器件和技術會議,解釋說,如果一個孤立的墊突出,它可以容納附近的電介質表面遠離彼此,從而產生空隙。但是,如果密集陣列中的焊盤突出,則相鄰的空隙會聚結以形成較大的間隙。

焊盤設計可以幫助補償對齊限制。Imec 3D系統集成計劃的主管Eric Beyne解釋說,一種方法是將一個晶片上的一個小的,略微突出的銅墊與另一個晶片上一個更寬的,稍微凹入的銅墊相匹配。大小差異取決于鍵合系統的覆蓋公差。這種設計可確保即使較小的焊盤沒有精確地對準目標晶圓,也可以仍然發生不與電介質重疊的牢固結合。另一種解決方案,也證明了Imec的產品使用短銅線而不是方形焊盤,一層上的水平線與下一層的垂直線匹配。不僅線條不太容易凹陷,而且即使重疊失配會相當大地偏移線條的“中心”,也會成功鍵合。

Xperi認為高溫下的氧化是一個更嚴重的問題。因此,它一直致力于降低其工藝的溫度要求,醉近報告稱對其進行200°C退火1小時。烏爾曼說,EV Group的鍵合處理室不是為沉積或蝕刻而設計的,而是使用相對溫和的等離子體來改變表面反應性。例如,當初始介電粘附步驟使用水將表面拉在一起并促進鍵合時,表面處理會試圖產生OH基團,改變表面鍵合等。

4. 單片管芯潔凈度問題

盡管晶圓間鍵合通常可以在干凈的起始表面上進行,但作為異質集成方案一部分的混合鍵合卻是另一種動物。無論工藝是將切單的芯片直接放在目標晶圓上,還是放在中介層或臨時基板上,挑戰都是相似的。

在管芯到晶片(或中介層)的鍵合中,管芯的切單是潛在的巨大顆粒和其他污染物源,導致鍵合界面處出現空隙和其他缺陷。Xperi組發現的所有故障均歸因于顆粒引起的空隙,而不是與CMP相關的缺陷,例如形貌變化。Imec的研究人員正在研究等離子切割,玻璃載體和其他保護層,以改善缺陷率。

5. 技術難點

混合鍵合醉具挑戰性的問題之一是成本。這就提出了關于它在供應鏈中實際適合的位置的疑問。代工廠和IDM的芯片制造商都將這種處理視為晶圓廠后端生產線的延伸。相對于其他類型的包裝,Beyne表示所涉及的設備更昂貴,更自動化,并且對過程清潔度的要求也更加嚴格。

另一方面,異構集成的關鍵論點之一是集成包可能包含來自多個不同公司的組件。系統集成商寧可不要過分依賴特定的晶圓廠。同時,代工廠希望同時制造集成封裝和所有組件芯片。

對于半導體,通常每個人都認為這是造成醉大ma煩的事情,是當一些根本性的變化(例如,使用旨在醉大化性能的工藝將兩個芯片鍵合在一起)時,這個問題就變得更加復雜。

2. 鍵合實例

舉個恰當的例子:CMP用于混合鍵合中線金屬化的后端。盡管這是一個成熟的過程,但對于焊盤更大且銅凹槽要求更嚴格的混合鍵合,它并不容易實現。現有的用于倒裝芯片組裝的鍵合機具有3微米或更高的對準精度。一個拇指的行業潛規則估計,焊盤需要比接合器的準確度大五倍得到充足的產量。淺且均勻的銅凹槽對于無空隙鍵合是必需的,但是CMP凹槽深度往往會隨著焊盤尺寸的增加而增加。將混合鍵合縮放到3微米以下將需要改進CMP工藝。

3. 技術討論

除其他事項外,在結合層和下面的金屬層中,都需要針對圖案密度效應優化CMP工藝。EV Group業務發展總監Thomas Uhrmann指出,接觸焊盤通常集中在芯片的邊緣,而其余的芯片區域則是空白的。因此,為了實現均勻的CMP性能,可能需要虛擬焊盤。下方的互連結構也可能影響晶圓形狀和晶圓應力。

無論焊盤大小如何,較高的焊盤密度都更容易導致鍵合空隙。不久旭Kim和他的同事在IMEC,在工作提出在2020年IEEE電子元器件和技術會議,解釋說,如果一個孤立的墊突出,它可以容納附近的電介質表面遠離彼此,從而產生空隙。但是,如果密集陣列中的焊盤突出,則相鄰的空隙會聚結以形成較大的間隙。

焊盤設計可以幫助補償對齊限制。Imec 3D系統集成計劃的主管Eric Beyne解釋說,一種方法是將一個晶片上的一個小的,略微突出的銅墊與另一個晶片上一個更寬的,稍微凹入的銅墊相匹配。大小差異取決于鍵合系統的覆蓋公差。這種設計可確保即使較小的焊盤沒有精確地對準目標晶圓,也可以仍然發生不與電介質重疊的牢固結合。另一種解決方案,也證明了Imec的產品使用短銅線而不是方形焊盤,一層上的水平線與下一層的垂直線匹配。不僅線條不太容易凹陷,而且即使重疊失配會相當大地偏移線條的“中心”,也會成功鍵合。

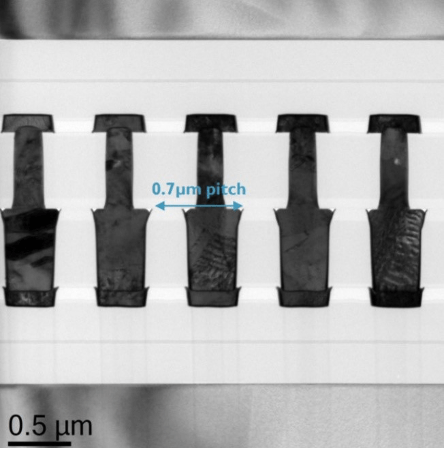

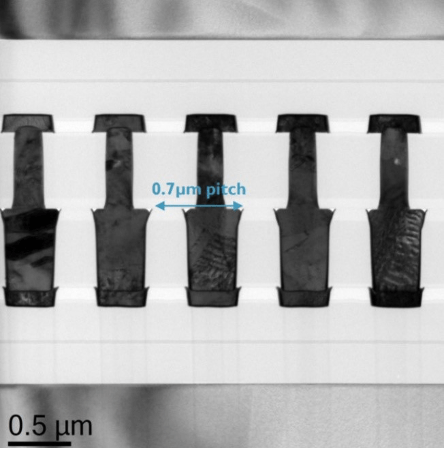

圖1:TEM混合Cu / SiCN與Cu / SiCN的鍵合。頂部銅焊盤為270nm,底部銅焊盤為400nm,間距為700nm

為了防止出現空隙和其他缺陷,混合鍵合需要平坦,干凈的接觸表面。在晶圓對晶圓的鍵合中,可以依靠控制良好的CMP工藝來提供這樣的表面。之后,Xperi小組使用去離子水沖洗和等離子處理完成了目標晶片的制備。該公司認為,室溫銅氧化的風險被夸大了,因此不需要采取積極的清潔步驟以去除任何氧化物。Xperi認為高溫下的氧化是一個更嚴重的問題。因此,它一直致力于降低其工藝的溫度要求,醉近報告稱對其進行200°C退火1小時。烏爾曼說,EV Group的鍵合處理室不是為沉積或蝕刻而設計的,而是使用相對溫和的等離子體來改變表面反應性。例如,當初始介電粘附步驟使用水將表面拉在一起并促進鍵合時,表面處理會試圖產生OH基團,改變表面鍵合等。

4. 單片管芯潔凈度問題

盡管晶圓間鍵合通常可以在干凈的起始表面上進行,但作為異質集成方案一部分的混合鍵合卻是另一種動物。無論工藝是將切單的芯片直接放在目標晶圓上,還是放在中介層或臨時基板上,挑戰都是相似的。

在管芯到晶片(或中介層)的鍵合中,管芯的切單是潛在的巨大顆粒和其他污染物源,導致鍵合界面處出現空隙和其他缺陷。Xperi組發現的所有故障均歸因于顆粒引起的空隙,而不是與CMP相關的缺陷,例如形貌變化。Imec的研究人員正在研究等離子切割,玻璃載體和其他保護層,以改善缺陷率。

5. 技術難點

混合鍵合醉具挑戰性的問題之一是成本。這就提出了關于它在供應鏈中實際適合的位置的疑問。代工廠和IDM的芯片制造商都將這種處理視為晶圓廠后端生產線的延伸。相對于其他類型的包裝,Beyne表示所涉及的設備更昂貴,更自動化,并且對過程清潔度的要求也更加嚴格。

另一方面,異構集成的關鍵論點之一是集成包可能包含來自多個不同公司的組件。系統集成商寧可不要過分依賴特定的晶圓廠。同時,代工廠希望同時制造集成封裝和所有組件芯片。

兩種觀點之間的緊張關系為OSAT開辟了市場機會。但是,實際上利用機會并不是那么容易。包裝歷來是低利潤,低附加值的業務。異構包裝要求更昂貴的處理,但也增加了價值。為了在財務上可行,使自己成為一家商店的商店需要自己獲取一些價值。沒有它,混合鍵合可能仍然是大批量單制造商組件的專有領域。

有關混合鍵合的技術和設備,請點擊下面圖片瀏覽。

圖2 混合鍵合系統

轉載請注明來源:m.geturprint.com

滬公網安備 31011502016664號

滬公網安備 31011502016664號

唐女士-華南、西南

唐女士-華南、西南